# **RETOKO**

## HIGH POWER FACTOR PREREGULATOR

### **FEATURES**

- Control Boost PWM to 0.99 Power Factor

- Limit Line Current Distortion to <5%

- World-Wide Operation Without Switches

- Feed-Forward Line Regulation

- Low Noise Sensitivity

- Pin Compatible With UC2854, and UC3854 (Licensed Source)

## DESCRIPTION

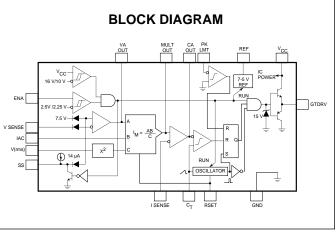

The TK83854 family of integrated circuits provide active power factor correction for power systems that otherwise would draw non-sinusoidal current from sinusoidal power lines. These parts implement all the control functions necessary to build a power supply preregulator capable of optimally using available power-line current while minimizing line-current distortion. To do this, the TK83854 contains a voltage amplifier, a precision analog multiplier/divider, a current amplifier, and a fixed-frequency PWM. In addition, the TK83854 contains a power MOSFET gate driver, 7.5 V reference, line anticipator, load-enable comparator, low supply detector, and over current comparator.

The TK83854 family uses average current mode control to accomplish fixed-frequency current control with stability and low distortion. Unlike peak current mode control, average current control accurately maintains sinusoidal line current without slope compensation.

The TK83854's high reference voltage and high oscillator amplitude minimize noise sensitivity while fast PWM elements permit chopping frequencies above 200 kHz. The TK83854 can be used in systems with line voltages that vary from 75 to 275 volts and with line frequencies across

# FEATURES (CONT.)

- Low Start-up Supply Current

- Fixed-Frequency PWM Drive

- Low-Offset Analog Multiplier/Divider

- 1 Amp Totem-Pole Gate Driver

- Precision Voltage Reference

the 50 Hz to 400 Hz range. To reduce the burden on the circuitry that supplies power to this device, the TK83854 family features low start-up supply current.

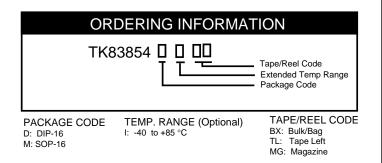

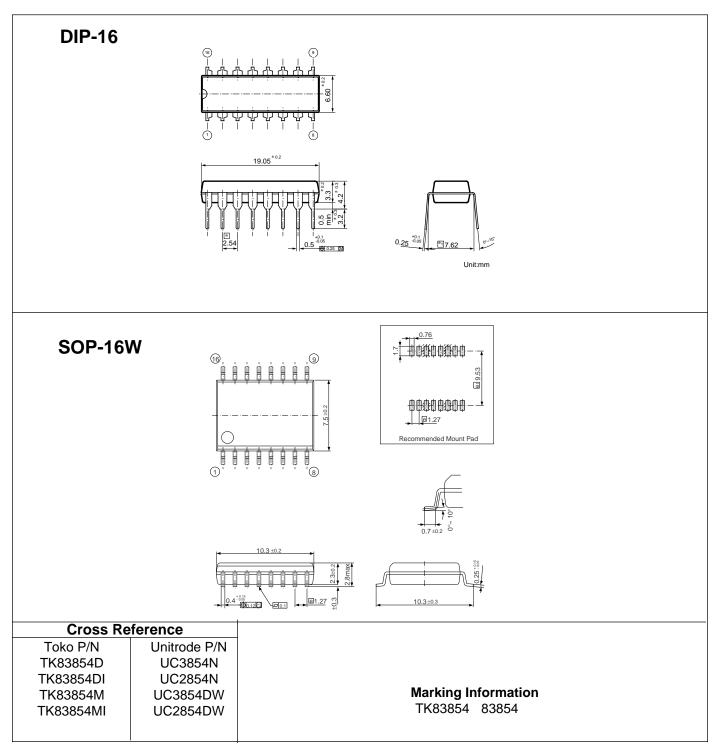

These devices are available in 16-pin plastic and 16 pin surface mount packages.

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage V <sub>CC</sub>      | 35 V  |

|-------------------------------------|-------|

| GTDRV Current, Continuous           | 0.5 A |

| GTDRV Current, 50% Duty Cycle       |       |

| Input Voltage, VSENSE, V(rms)       | 11 V  |

| Input Voltage, ENA, ISENSE, MULTOUT | 11 V  |

| Input Voltage, PKLMT                | 5 V   |

| Input Current, RSET, IAC, PKLMT     |       |

| Power Dissipation (Plastic DIP) (Note 1)1 W |               |

|---------------------------------------------|---------------|

| Power Dissipation (SOIC-16W) (Note 2)750 mW | 750 mW        |

| Operating Temperature Range                 |               |

| (Commercial)0 to +70 °C                     | . 0 to +70 °C |

| (Industrial)40 to +85 °C                    | 40 to +85 °C  |

#### **ELECTRICAL CHARACTERISTICS**

Test conditions:  $V_{CC} = 18 \text{ V}, \text{ R}_{SET} = 15 \text{ k}$  to Ground,  $C_T = 1.5 \text{ nF}, \text{ V}_{(PKLMT)} = 1 \text{ V}, \text{ ENA} = 7.5 \text{ V}, \text{ V}_{(RMS)} = 1.5 \text{ V}, \text{ I}_{(IAC)} = 100 \,\mu\text{A}, \text{ V}_{(ISENSE)} = 0 \text{ V}, \text{ V}_{OUT(CA)} = 3.5 \text{ V}, \text{ V}_{OUT(VA)} = 5 \text{ V}, \text{ V}_{SENSE} = 7.5 \text{ V}, \text{ No load on SS}, \text{ CA}_{OUT}, \text{ VA}_{OUT}, \text{ REF}, \text{ GTDRV}, \text{ T}_{A} = \text{Operating Range, unless otherwise specified.}$

| SYMBOL                 | PARAMETER                            | TEST CONDITIONS | MIN  | ТҮР        | MAX  | UNITS |

|------------------------|--------------------------------------|-----------------|------|------------|------|-------|

| I <sub>CC(OFF)</sub>   | Supply Current, Off                  | ENA = 0 V       |      | 1.5        | 2.0  | mA    |

| I <sub>CC(ON)</sub>    | Supply Current, On                   |                 |      | 10         | 16   | mA    |

| UVLO <sub>(ON)</sub>   | V <sub>CC</sub> Turn-On Threshold    |                 | 14.5 | 16         | 17.5 | V     |

| UVLO <sub>(OFF)</sub>  | V <sub>CC</sub> Turn-Off Threshold   |                 | 9    | 10         | 11   | V     |

| V <sub>ENA</sub>       | Enable Threshold, Rising             |                 | 2.4  | 2.55       | 2.7  | V     |

| V <sub>ENA(HYST)</sub> | Enable Threshold Hysteresis          |                 | 0.2  | 0.25       | 0.3  | V     |

| I <sub>ENA</sub>       | Enable Input Current                 | ENA = 0 V       | -5.0 | -0.2       | 5.0  | μΑ    |

| I <sub>V(rms)</sub>    | V(rms) Input Current                 | V(rms) = 5 V    | -1.0 | -0.01      | 1.0  | μΑ    |

| Voltage Amp            | lifier                               |                 |      |            |      | 1     |

| V <sub>OS(VA)</sub>    | Voltage Amp Offset Voltage           | VAOUT = 5 V     | -8   |            | 8    | mV    |

| I <sub>B(VA)</sub>     | VSENSE Bias Current                  |                 | -500 | -25        | 500  | nA    |

| A <sub>OL(VA)</sub>    | Voltage Amp Gain                     |                 | 70   | 100        |      | dB    |

| $\Delta V_{OUT(VA)}$   | Voltage Amp Output Swing             |                 |      | 0.5 to 5.8 |      | V     |

| I <sub>SC(VA)</sub>    | Voltage Amp Short Circuit<br>Current | VAOUT = 0 V     | -30  | -12        | -5   | mA    |

| I <sub>SS</sub>        | SS Current                           | SS = 2.5 V      | -20  | -14        | -6   | μA    |

| Current Amp            | lifier                               |                 | I    |            |      | 1     |

| V <sub>OS(CA)</sub>    | Current Amp Offset Voltage           |                 | -4   |            | 4    | mV    |

| I <sub>B(CA)</sub>     | ISENSE Bias Current                  |                 | -500 | -120       | 500  | nA    |

| A <sub>OL(CA)</sub>    | Current Amp Gain                     |                 | 80   | 110        |      | dB    |

| $\Delta V_{OUT(CA)}$   | Current Amp Output Swing             |                 |      | 0.5 to 16  |      | V     |

Note 1: Power dissipation must be derated at the rate of 8 mW/°C for operation above 25 °C.

Note 2: Power dissipation must be derated at the rate of 3.3 mW/°C for operation above 25 °C.

Note 3: All voltages with respect to GND (Pin 1).

Note 4: All currents are positive into the specified terminal.

## **ELECTRICAL CHARACTERISTICS (CONT.)**

Test conditions :  $V_{CC} = 18 \text{ V}, \text{ R}_{SET} = 15 \text{ k}$  to Ground,  $C_T = 1.5 \text{ nF}, V_{(PKLMT)} = 1 \text{ V}, \text{ ENA} = 7.5 \text{ V}, V_{(RMS)} = 1.5 \text{ V}, I_{(IAC)} = 100 \,\mu\text{A}, V_{(ISENSE)} = 0 \text{ V}, V_{OUT(CA)} = 3.5 \text{ V}, V_{OUT(VA)} = 5 \text{ V}, V_{SENSE} = 7.5 \text{ V}, \text{ No load on SS}, CA_{OUT}, VA_{OUT}, \text{REF}, \text{GTDRV}, T_A = \text{Operating Range, unless otherwise specified.}$

| SYMBOL                 | PARAMETER                              | TEST CONDITIONS                                 | MIN            | ТҮР  | MAX  | UNITS |

|------------------------|----------------------------------------|-------------------------------------------------|----------------|------|------|-------|

| Current Ampl           | ifier                                  |                                                 | II             |      |      | 1     |

| I <sub>SC(CA)</sub>    | Current Amp Short Circuit<br>Current   | CAOUT = 0 V                                     | -30            | -12  | -5   | mA    |

| V <sub>(ISENSE)</sub>  | Input Range, ISENSE,<br>MULTOUT        |                                                 | -0.3 to<br>2.5 |      |      | V     |

| GBW                    | Current Amp Gain-BW Product            | T <sub>A</sub> = 25 °C (Note 6)                 | 400            | 800  |      | kHz   |

| Reference              |                                        |                                                 | 11             |      |      |       |

| V <sub>REF</sub>       | Reference Output Voltage               | I <sub>REF</sub> = 0 mA, T <sub>A</sub> = 25 °C | 7.4            | 7.5  | 7.6  | V     |

|                        |                                        | I <sub>REF</sub> = 0 mA, Over Temp              | 7.35           | 7.5  | 7.65 | V     |

| $\Delta V_{REF(LOAD)}$ | V <sub>REF</sub> Load Regulation       | -10 mA <i<sub>REF&lt;0 mA</i<sub>               | -15            | 5    | 15   | mV    |

| $\Delta V_{REF(LINE)}$ | V <sub>REF</sub> Line Regulation       | 15 V <v<sub>CC&lt;35 V</v<sub>                  | -10            | 2    | 10   | mV    |

| I <sub>REF(SC)</sub>   | V <sub>REF</sub> Short Circuit Current | REF = 0 V                                       | -50            | -28  | -12  | mA    |

| Peak Limit             |                                        |                                                 |                |      |      |       |

| V <sub>OS(PL)</sub>    | PKLMT Offset Voltage                   |                                                 | -10            |      | 10   | mV    |

| I <sub>B(PL)</sub>     | PKLMT Input Current                    | PKLMT = -0.1 V                                  | -200           | -100 |      | μA    |

| t <sub>D(PL)</sub>     | PKLMT to GTDRV Prop.<br>Delay          | PKLMT falling from 50 mV<br>to -50 mV           |                | 175  |      | ns    |

| Gate Driver            |                                        |                                                 | 11             | l    |      |       |

| V <sub>G(MAX)</sub>    | Maximum GTDRV Output<br>Voltage        | No load,<br>18 V <v<sub>CC&lt;35 V</v<sub>      | 13             | 14.5 | 18   | V     |

| V <sub>GH</sub>        | GTDRV Output Voltage High              | 200 mA source,<br>V <sub>CC</sub> = 15 V        | 12             | 12.8 |      | V     |

| V <sub>GL(OFF)</sub>   | GTDRV Output Voltage Low,<br>OFF       | $V_{CC} = 0 V, 50 mA sink$                      |                | 0.9  | 1.5  | V     |

| V <sub>GL</sub>        | GTDRV Output Voltage Low               | 200 mA sink                                     |                | 1.0  | 2.2  | V     |

| -                      |                                        | 10 mA sink                                      |                | 0.1  | 0.4  | V     |

| I <sub>G(PK)</sub>     | Peak GTDRV Current                     | 10 nF load                                      |                | 1.0  |      | A     |

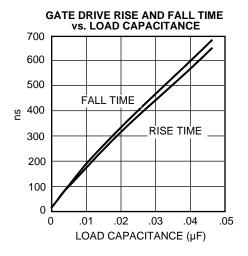

| $t_{R(G)}/t_{F(G)}$    | GTDRV Rise/Fall Time                   | 1 nF load                                       |                | 35   |      | ns    |

| D <sub>MAX</sub>       | GTDRV Maximum Duty Cycle               | CA <sub>OUT</sub> = 7 V                         |                | 95   |      | %     |

Note 5: ENA input is internally clamped to approximately 14 V.

Note 6: Guaranteed by design; not 100% tested.

## **ELECTRICAL CHARACTERISTICS (CONT.)**

Test conditions :  $V_{CC} = 18 \text{ V}, \text{ R}_{SET} = 15 \text{ k}$  to Ground,  $C_T = 1.5 \text{ nF}, V_{(PKLMT)} = 1 \text{ V}, \text{ ENA} = 7.5 \text{ V}, V_{(RMS)} = 1.5 \text{ V}, I_{(IAC)} = 100 \,\mu\text{A}, V_{(ISENSE)} = 0 \text{ V}, V_{OUT(CA)} = 3.5 \text{ V}, V_{OUT(VA)} = 5 \text{ V}, V_{SENSE} = 7.5 \text{ V}, \text{ No load on SS}, CA_{OUT}, VA_{OUT}, REF, GTDRV, T_A = Operating Range, unless otherwise specified.}$

| SYMBOL               | PARAMETER                                               | TEST CONDITIONS                                                     | MIN  | ТҮР  | MAX  | UNITS |

|----------------------|---------------------------------------------------------|---------------------------------------------------------------------|------|------|------|-------|

| Multiplier           |                                                         |                                                                     |      |      |      | 1     |

| I <sub>OM(IAC)</sub> | Multiplier Output Current (IAC Limited)                 | IAC = 100 μA, R <sub>SET</sub> = 10 k                               | -220 | -200 | -180 | μA    |

| I <sub>OM(ZC)</sub>  | Multiplier Output Current Zero                          | IAC = 0 μA, R <sub>SET</sub> = 15 k                                 | -2.0 | -0.2 | 2.0  | μA    |

| I <sub>OM(SET)</sub> | Multiplier Output Current<br>(R <sub>SET</sub> limited) | IAC = 450 $\mu$ A, R <sub>SET</sub> = 15 k<br>V(rms) = 1 V,VA = 6 V | -280 | -255 | -220 | μA    |

| I <sub>OM</sub>      | Multiplier Output Current                               | IAC = 50 μA,<br>V(rms) = 2 V,VA = 4 V                               | -50  | -42  | -33  | μA    |

| I <sub>OM</sub>      | Multiplier Output Current                               | IAC = 100 μA,<br>V(rms) = 2 V, VA = 2 V                             | -38  | -27  | -12  | μA    |

| I <sub>OM</sub>      | Multiplier Output Current                               | IAC = 200 μA,<br>V(rms) = 2 V, VA = 4 V                             | -165 | -150 | -105 | μA    |

| I <sub>OM</sub>      | Multiplier Output Current                               | IAC = 300 μA,<br>V(rms) =1 V, VA = 2 V                              | -250 | -225 | -150 | μA    |

| I <sub>OM</sub>      | Multiplier Output Current                               | $IAC = 100 \ \mu A,$<br>V(rms) =1 V, V <sub>A</sub> = 2 V           | -95  | -80  | -60  | μA    |

| К                    | Multiplier Gain Constant                                | See Note 7                                                          |      | -1.0 |      | V     |

| Oscillator           |                                                         | · · · · · · · · · · · · · · · · · · ·                               |      |      |      |       |

| f <sub>OSC</sub>     | Oscillator Frequency                                    | R <sub>SET</sub> = 15 K                                             | 46   | 55   | 62   | kHz   |

|                      |                                                         | R <sub>SET</sub> = 8.2 K                                            | 86   | 102  | 118  | kHz   |

| V <sub>RP</sub>      | C <sub>T</sub> Ramp Peak-to-Peak<br>Amplitude           |                                                                     | 4.9  | 5.4  | 5.9  | V     |

| V <sub>RV</sub>      | C <sub>T</sub> Ramp Valley Voltage                      |                                                                     | 0.8  | 1.1  | 1.3  | V     |

|                      |                                                         |                                                                     |      |      | 1    | 1     |

Note 7: Multiplier Gain Constant (K) is defined by the following equation:  $I_{OM} = \frac{K * I_{(IAC)} * (V_{OUT(VA)} - 1)}{K * I_{(IAC)} * (V_{OUT(VA)} - 1)}$

V(rms)<sup>2</sup>

#### **PIN DESCRIPTIONS**

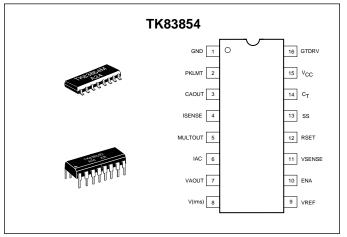

**GND** (Pin 1) (Ground): All voltages are measured with respect to GND. VCC and REF should be bypassed directly to GND with a 0.1  $\mu$ F or larger ceramic capacitor. The timing capacitor discharge current also returns to this pin, so the lead from the oscillator timing capacitor to GND should also be as short and as direct as possible.

**PKLMT** (Pin 2) (Peak Limit): The threshold for PKLMT is GND. Connect this input to the negative voltage on the current sense resistor as shown in Figure 1. Use a resistor to REF to offset the negative current sense signal up to GND.

**CAOUT** (Pin 3) (Current Amplifier Output): This is the output of a wide-bandwidth opamp that senses line current and commands the pulse width modulator (PWM) to force the correct current. This output can swing close to GND, allowing the PWM to force zero duty cycle when necessary. The current amplifier will remain active even if the IC is disabled.

**ISENSE** (Pin 4) (Current Sense Minus): This is the inverting input to the current amplifier. This input and the non-inverting input MULTOUT remain functional down to and below GND. Care should be taken to avoid taking these inputs below –0.5 V, because they are protected with diodes to GND.

## **PIN DESCRIPTIONS (CONT.)**

**MULTOUT** (Pin 5) (Multiplier Output and Current Sense Plus): The output of the analog multiplier and the noninverting input of the current amplifier are connected together at MULTOUT. The cautions about taking ISENSE below -0.5 V also apply to MULTOUT. As the multiplier output is a current, this is a high impedance input similar to ISENSE, so the current amplifier can be configured as a differential amplifier to reject GND noise. The test circuit shows an example of using the current amplifier differentially.

**IAC** (Pin 6) (Input AC Current): This input to the analog multiplier is a current. The multiplier is tailored for very low distortion from this current input (IAC) to MULTOUT), so this is the only multiplier input that should be used for sensing instantaneous line voltage. The nominal voltage on IAC is 6 V, so in addition to a resistor from IAC to rectified line, connect a resistor from IAC to REF. If the resistor to REF is one fourth of the value of the resistor to the rectifier, then the 6 V offset will be cancelled, and the line current will have minimal cross-over distortion.

**VAOUT** (Pin 7) (Voltage Amplifier Output): This is the output of the opamp that regulates output voltage. Like the current amplifier, the voltage amplifier will also stay active even if the IC is disabled with either ENA or  $V_{CC}$ . This means that large feedback capacitors across the amplifier will stay charged through momentary disable cycles. Voltage amplifier output levels below ~1 V will inhibit multiplier output.

**V(rms)** (Pin 8) (RMS Line Voltage): The output of a boost PWM is proportional to the input voltage, so when the line voltage into a low-bandwidth boost PWM voltage regulator changes, the output will change immediately and slowly recover to the regulated level. For these devices, the V(rms) input compensates for line voltage changes if it is connected to a voltage proportional to the RMS input line voltage. For best control, the V(rms) voltage should stay between 1.5 V and 3.5 V.

**REF** (Pin 9) (Voltage Reference Output): REF is the output of an accurate 7.5 V voltage reference. This output is capable of delivering 10 mA to peripheral circuitry and is internally short circuit current limited. REF is disabled and will remain at 0 V when  $V_{CC}$  is low or when ENA is low. Bypass REF to GND with an 0.1  $\mu$ F or larger ceramic capacitor for best stability.

**ENA** (Pin 10) (Enable): ENA is a logic input that will enable the PWM output, voltage reference, and oscillator. ENA

also will release the soft start clamp, allowing SS to rise. When unused, connect ENA to a +5 V supply or pull ENA high with a 22 k resistor. The ENA pin is not intended to be used as a high speed shutdown to the GTDRV output.

**VSENSE** (Pin 11) (Voltage Amplifier Inverting Input): This is normally connected to a feedback network and to the boost converter output through a divider network.

**RSET** (Pin 12) (Oscillator Charging Current and Multiplier Limit Set): A resistor from  $R_{SET}$  to ground will program oscillator charging current and maximum multiplier output. Multiplier output current will not exceed 3.75 V divided by the resistor from  $R_{SET}$  to ground.

**SS** (Pin 13) (Soft Start): SS will remain at GND as long as the IC is disabled or  $V_{CC}$  is too low. SS will pull up to over 8 V by an internal 14  $\mu$ A current source when both  $V_{CC}$  becomes valid and the IC is enabled. SS will act as the reference input to the voltage amplifier if SS is below REF. With a large capacitor from SS to GND, the reference to the voltage regulating amplifier will rise slowly, and increase the PWM duty cycle slowly. In the event of a disable command or a supply dropout, SS will quickly discharge to ground and disable the PWM.

$C_T$ (Pin 14) (Oscillator Timing Capacitor): A capacitor from  $C_T$  to GND will set the PWM oscillator frequency according to this relationship:

$$f_{OSC} = \frac{1.25}{R_{SET}C_T}$$

$\mathbf{V_{CC}}$  (Pin 15) (Positive Supply Voltage): Connect  $V_{CC}$  to a stable source of at least 20 mA above 17 V for normal operation. Also bypass  $V_{CC}$  directly to GND to absorb supply current spikes required to charge external MOSFET gate capacitances. To prevent inadequate GTDRV signals, these devices will be inhibited unless  $V_{CC}$  exceeds the upper under-voltage lockout threshold and remains above the lower threshold.

**GTDRV** (Pin 16) (Gate Driver): The output of the PWM is a totem pole MOSFET gate driver on GTDRV. This output is internally clamped to 15 V so that the IC can be operated with  $V_{CC}$  as high as 35 V. Use a series gate resistor of at least 5 ohms to prevent interaction between the gate impedance and the GTDRV output driver that might cause the GTDRV output to overshoot excessively. Some overshoot of the GTDRV output is always expected when driving a capacitive load.

## **TYPICAL APPLICATIONS**

#### A 250 W PREREGULATOR

SS (Soft Start)

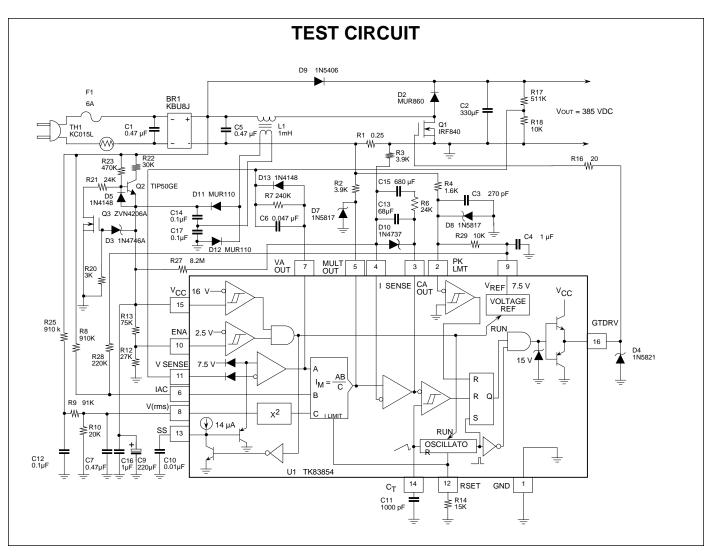

The test circuit shows a typical application of the TK83854 as a preregulator with high power factor and efficiency. The assembly consists of two distinct parts, the control circuit centering on the TK83854 and the power section.

The power section is a "boost" converter, with the inductor operating in the continuous mode. In this mode, the duty cycle is dependent on the ratio between input and output voltages, also, the input current has low switching frequency ripple, which means that the line noise is low. Furthermore, the output voltage must be higher than the peak value of the highest expected AC line voltage, and all components must be rated accordingly.

In the control section, the TK83854 provides PWM pulses to the power MOSFET gate (GTDRV, Pin 16). The duty cycle of this output is simultaneously controlled by four separate inputs to the chip:

| INPUT          | PIN # | FUNCTION              |

|----------------|-------|-----------------------|

| VSENSE         | 11    | Output DC Voltage     |

| IAC            | 6     | Line Voltage Waveform |

| ISENSE/MULTOUT | 4/5   | Line Current          |

| V(rms)         | 8     | RMS Line Voltage      |

Additional controls of an auxiliary nature are provided. They are intended to protect the switching power MOSFETS from certain transient conditions, as follows:

| INPUT | PIN # | FUNCTION              |

|-------|-------|-----------------------|

| ENA   | 10    | Start-Up Delay        |

| SS    | 13    | Soft Start            |

| PKLMT | 2     | Maximum Current Limit |

#### **PROTECTION INPUTS**

#### ENA (Enable)

The ENA input must reach 2.5 volts before the REF and GTDRV outputs are enabled. This provides a means to shut down the gate in case of trouble, or to add a time delay at power up. A hysteresis gap of 200 mV is provided at this terminal to prevent erratic operation. Undervoltage protection is provided directly at pin 15, where the on/off thresholds are 16 V and 10 V.

The voltage at pin 13 (SS) can reduce the reference voltage used by the error amplifier to regulate the output DC voltage. With pin 13 open, the reference voltage is typically 7.5 V. An internal current source delivers approximately 14  $\mu$ A from pin 13. Thus a capacitor connected between that pin and ground will charge linearly from zero to 7.5 V in 0.54 \* C seconds, with C expressed in microfarads.

PKLMT (Peak Current Limit)

Use pin 2 to establish the highest value of current to be controlled by the power MOSFET. With the resistor divider values shown in the test circuit, the 0.0 V threshold at pin 2 is reached when the voltage drop across the 0.25  $\Omega$  current sense resistor is 7.5 V \* 1.6 k/10 k = 1.2 V, corresponding to 4.8 A. A bypass capacitor from pin 2 to ground is recommended to filter out very high frequency noise.

#### **CONTROL INPUTS**

VSENSE (Output DC Voltage Sense)

The threshold voltage for the VSENSE input is 7.5 V and the input bias current is typically -10 nA. The values shown in the test circuit are for an output voltage of 400 VDC. In this circuit, the voltage amplifier operates with a constant low frequency gain for minimum output excursions. The 47 nF feedback capacitor places a 15 Hz pole in the voltage loop that prevents 120 Hz ripple from propagating to the output current.

#### IAC (Line Waveform)

In order to force the line current waveshape to follow the line voltage, a sample of the power line voltage waveform is introduced at pin 6. This signal is multiplied by the output of the voltage amplifier in the internal multiplier to generate a reference signal for the current control loop.

This input is not a voltage, but a current (hence IAC). It is set up by the 220 k and 910 k resistive divider (see test circuit). The voltage at pin 6 is internally held at 6 V, and the two resistors are chosen so that the current flowing into pin 6 varies from zero (at each zero crossing) to about 400  $\mu$ A at the peak of the waveshape. The following formulas were

## **TYPICAL APPLICATIONS (CONT.)**

used to calculate these resistors:

$R_{REF} = R_{IAC} / 4 = 220 \text{ k}$ (where Vpk is the peak line voltage)

#### ISENSE/MULTOUT (Line Current)

The voltage drop across the 0.25  $\Omega$  current-sense resistor is applied to pins 4 and 5 as shown. The current-sense amplifier also operates with high low-frequency gain, but unlike the voltage amplifier, it is set up to give the currentcontrol loop a very wide bandwidth. This enables the line current to follow the line voltage as closely as possible. In the present example, this amplifier has a zero at about 500 Hz, and a gain of about 18 dB thereafter.

#### V(rms) (RMS Line Voltage)

An important feature of the TK83854 preregulator is that it can operate with a three-to-one range of input line voltages, covering everything from low line in Japan (85 VAC) to high line in Europe (255 VAC). This is done using line feedforward, which keeps the input power constant with varying input voltage (assuming constant load power). To do this, the multiplier divides the line current by the square of the rms value of the line voltage. The voltage applied to pin 8, proportional to the average of the rectified line voltage (and proportional to the RMS value), is squared in the TK83854, and then used as a divisor by the multiplier block. The multiplier output, at pin 5, is a current that increases with the current at pin 6 and the voltage at pin 7, and decreases with the square of the voltage at pin 8.

#### **PWM Frequency**

The PWM oscillator frequency in the test circuit is 100 kHz. This value is determined by  $C_T$  at pin 14 and  $R_{SET}$  at pin 12.  $R_{SET}$  should be chosen first because it affects the maximum value of  $I_{OM}$  according to the equation:

$$I_{OM(MAX)} = \frac{-3.75V}{R_{SET}}$$

This effectively sets a maximum PWM-controlled current. With  $R_{SFT} = 15 \text{ k}$ ,

$$I_{OM(MAX)} = -\frac{-3.75 \text{ V}}{15 \text{ k}} = -250 \text{ }\mu\text{A}$$

It is also important to note that the multiplier output current will never exceed twice IAC.

With the 3.9 k resistor from MULTOUT to the 0.25  $\Omega$  current sense resistor, the maximum current in the current sense resistor will be

$$I_{\text{RCS(MAX)}} = \frac{-I_{\text{OM(MAX)}} * 3.9 \text{ k}}{0.25 \Omega} = -3.9 \text{ Amp}$$

Having thus selected  $\mathsf{R}_{\mathsf{SET}}$ , the current sense resistor, and the resistor from MULTOUT to the current sense resistor, calculate  $\mathsf{C}_{\mathsf{T}}$  for the desired PWM oscillator frequency from the equation

$$C_{T} = \frac{1.25}{f_{OSC} * R_{SET}}$$

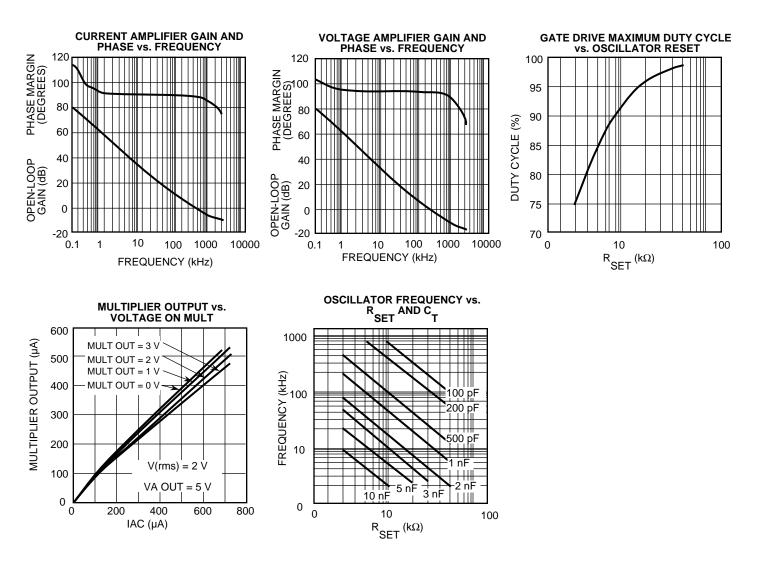

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A$  - 25 °C, unless otherwise specified

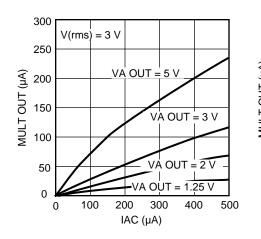

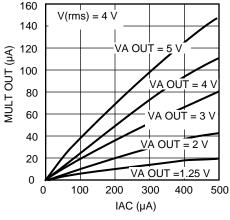

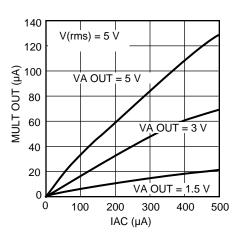

## **TYPICAL PERFORMANCE CHARACTERISTICS (CONT.)**

$T_A = 25 \ ^{\circ}C$ , unless otherwise specified

#### Multiplier Output vs Multiplier Inputs with Mult Out = 0 V

## PACKAGE OUTLINES

The information furnished by TOKO, Inc. is believed to be accurate and reliable. However, TOKO reserves the right to make changes or improvements in the design, specification or manufacture of its products without further notice. TOKO does not assume any liability arising from the application or use of any product or circuit described herein, nor for any infringements of patents or other rights of third parties which may result from the use of its products. No license is granted by implication or otherwise under any patent or patent rights of TOKO, Inc.

NOTES

#### **TOKO AMERICA REGIONAL OFFICES**

#### Midwest Regional Office

Toko America, Inc. 1250 Feehanville Drive Mount Prospect, II 60056 Tel: (847) 297-0070 Fax: (847) 699-7864

#### Western Regional Office Toko America, Inc. 2480 North First Street, Suite 260 San Jose, CA 95131 Tel: (408) 432-8281 Fax: (408) 943-9790

## Eastern Regional Office

Toko America, Inc. 107 Mill Plain Road Danbury, CT 06811 Tel: (203) 748-6871 Fax: (203) 797-1223

#### Semiconductor Technical Support Toko Design Center 4755 Forge Road Colorado Springs, CO 80907 Tel: (719) 528-2200

Fax: (719) 528-2375

IC-167-TK83854

#### http://www.tokoam.com

Page 12 © 1997 Toko, Inc. All rights reserved Printed in the USA